yuzuha_wasa/未来の扉を開けて

分类

标签

Apache apt Blogging Customization C语言 Demo DMA Example F4A0 F5529 FPGA Fuwari G2553 git GPIO HC-05 HC-06 HC32 HDSC IAP Keil Linux基础知识 Linux安全 Linux常用命令 Linux文件与目录管理 Linux文件全线管理 Linux文件操作 Linux用户管理 Linux的C语言编程 Linux系统监测 Linux项目 Manjaro mariadb Markdown matlab MCU MSP430 Nginx Nvidia openSUSE OSS phpmyadmin PWM Python Quartus RT-Thread Service SPI ST STM32 systemctl systemd TI Timer Typora Ubuntu Video VideoDecode zypper 中断系统 压缩包 图床 外部中断 定时器 定时器输入捕获 帮助命令 常用命令 开发环境 归档 数据库 数据结构 数据绘图 状态监控 编码器 网络基础知识 网络工具 蓝牙模块 虚拟机 资源分享 软件包管理器 邮箱服务器 防火墙

557 字

3 分钟

HC32F4A0 SPI及其DMA

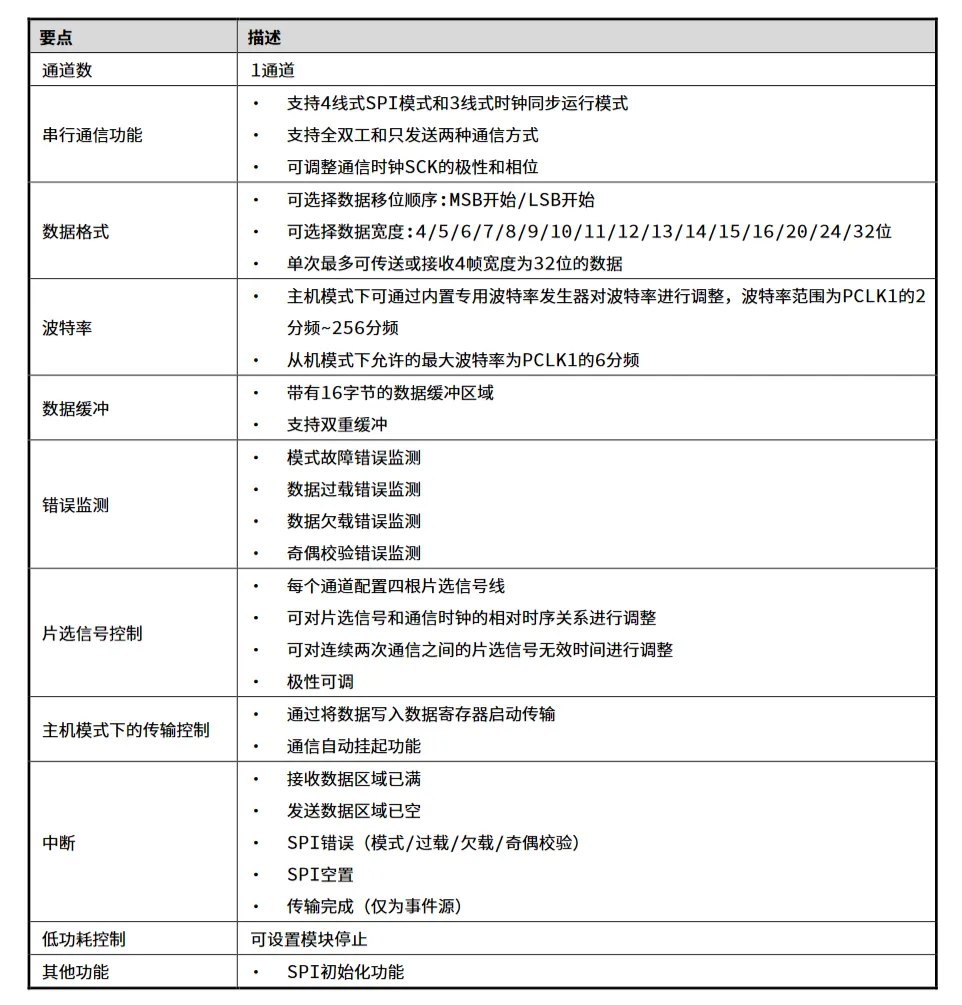

支持特性

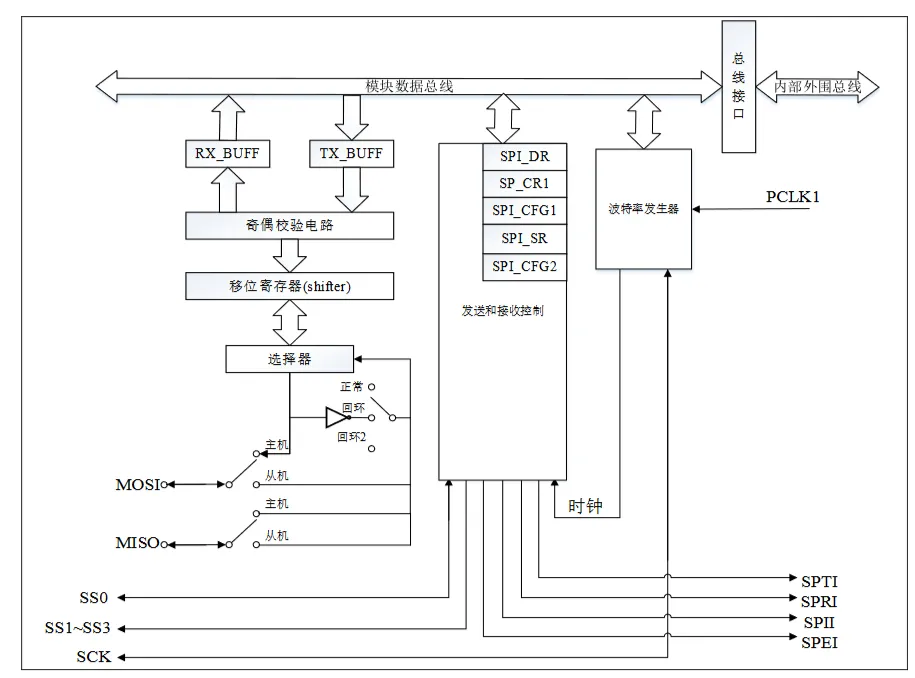

系统框图

从下图来看,波特率发生器产生的SCLK信号由PCLK1时钟生成

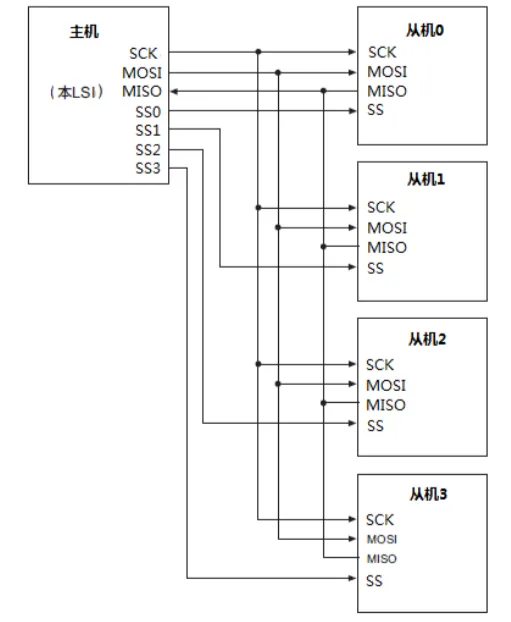

连接模式

模式由应用场景决定,常用习惯为四线式用在MCU发送,三线式用在MCU接收

连接模式的设置由由

stc_spi_init_t的成员变量u32WireMode控制

四线式

即SCLK、SS、MISO、MOSI

文档中的主机模式

三线式

即SCLK、MISO、MOSI,取消使用ss,使用此模式片选手动设置GPIO电平管理

此模式的妙用为:设置为此模式并设置MCU为从机模式,使用GPIO检查模组的SS电平便可以判断一帧数据帧是否发送完毕,以便进行下一步操作

文档中的时钟同步运行,并非网上所说的半双工的

三线制,三线制为MISO、MOSI复用但是依然有片选控制引脚

主从模式

无论主从机管脚输入类型请设定为 CMOS 输入,输出请设定为高驱动力模式,设定请参照【通用 IO(GPIO)】章节通用 IO 特殊寄存器 PCR。

波特率

当工作在主机模式,时钟由波特率发生器生成,时钟为PCLK1分频

分频由

stc_spi_init_t的成员变量u32BaudRatePrescaler控制

数据格式

奇偶校验

奇偶校验由

stc_spi_init_t的成员变量u32Parity控制

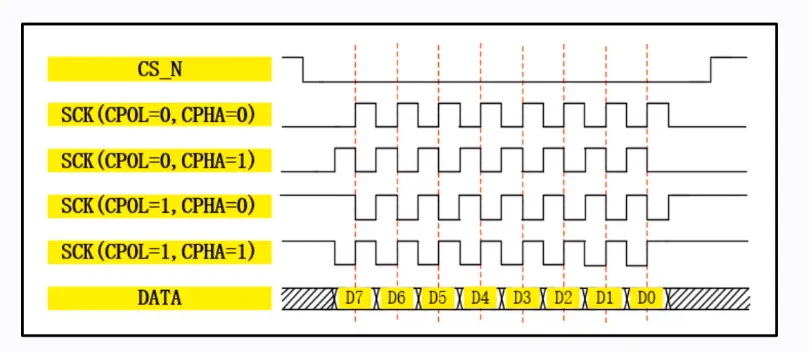

四种工作模式

时钟极性(CPOL)

- CPOL = 0: 表示时钟在空闲状态时为低电平。当SPI通信开始时,时钟将从低变高。

- CPOL = 1: 表示时钟在空闲状态时为高电平。当SPI通信开始时,时钟将从高变低。

时钟相位(CPHA)

- CPHA = 0: 表示数据在时钟的第一个边沿(对于CPOL=0是上升沿,对于CPOL=1是下降沿)被采样。

- CPHA = 1: 表示数据在时钟的第二个边沿(对于CPOL=0是下降沿,对于CPOL=1是上升沿)被采样。这意味着数据需要在当前时钟周期的第一个边沿之后准备好。

一般常用模式0(flash) /模式1(外设),下图引用自通信协议(二)——SPI协议-网速123

四种工作模式的设置由由

stc_spi_init_t的成员变量u32SpiMode控制

HC32F4A0 SPI及其DMA

https://kozakemi.top/posts/hc32f4a0-spi及其dma/